# **Applications Note: SY5002C**

**Flyback Controller**

With Primary Side CV/CC Control For Adapters and Chargers

### **General Description**

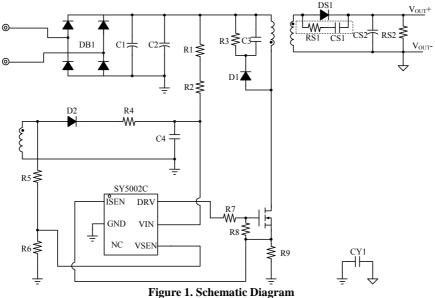

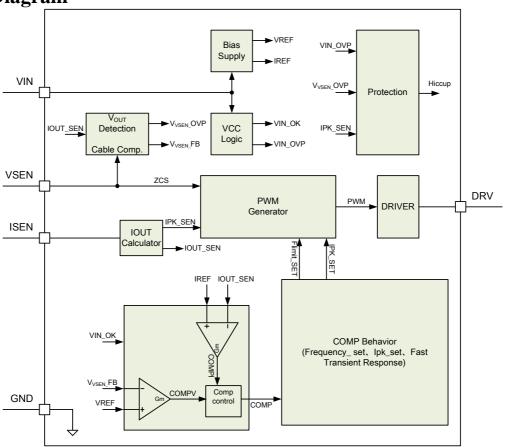

SY5002C is a single stage Flyback controller targeting at Constant Current / Constant Voltage (CC/CV) applications. Both current and voltage regulation are achieved by primary side control technology for low cost application. To achieve higher efficiency and better EMI performance, SY5002C drives Flyback converters in the Quasi-Resonant mode and adaptive PWM/PFM control. In addition, SY5002C has cable compensation to regulate the output voltage for better load regulation at cable terminal.

### **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY5002CABC      | SOT23-6      |      |

### **Features**

- Primary side CV/CC control eliminates the optocoupler.

- Valley turn-on of the primary MOSFET to achieve low switching losses

- Internal CC/CV loop compensation

- The self-adaption compensation for better stability

- PWM/PFM control for higher average efficiency

- Fast dynamic load transient response

- Cable compensation for better load regulation

- Low start up current: 4μA Max

- · Reliable protections for OVP, SCP, OTP

- Reliable protections for safety requirement

- Maximum switching frequency limitation 125kHz

- Compact package: SOT23-6

### **Applications**

- AC/DC adapters

- · Battery Chargers

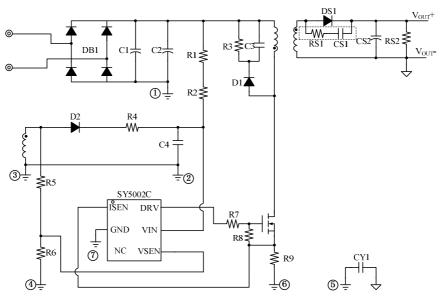

# **Typical Applications**

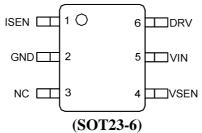

### Pinout (top view)

Top Mark: ZSxyz (device code: ZS, x=year code, y=week code, z= lot number code)

| Pin | Name | Description                                                                                                 |

|-----|------|-------------------------------------------------------------------------------------------------------------|

| 1   | ISEN | Current sense pin. Connect this pin to the source of the primary switch.                                    |

| 2   | GND  | Ground pin.                                                                                                 |

| 3   | NC   | Not used                                                                                                    |

| 4   | VSEN | Inductor current zero-crossing detection pin. This pin receives the auxiliary winding voltage by a resistor |

| 4   | VSEN | divider and detects the inductor current zero crossing point.                                               |

| 5   | VIN  | Power supply pin.                                                                                           |

| 6   | DRV  | Gate driver pin. Connect this pin to the gate of primary MOSFET.                                            |

Absolute Maximum Ratings (Note 1) Supply Current I<sub>VIN</sub> -----ISEN, COMP -----Power Dissipation, @ TA = 25°C SOT23-6 -----Package Thermal Resistance (Note 2) SOT23-6,  $\theta_{JA}$  ------ 170°C/W SOT23-6, θ<sub>JC</sub> -------130°C/W Lead Temperature (Soldering, 10 sec.) ------ 260°C **Recommended Operating Conditions** (Note 3)

Junction Temperature Range -----Ambient Temperature Range -----

### **Block Diagram**

### **Electrical Characteristics**

$(V_{IN} = 12V \text{ (Note 3)}, T_A = 25^{\circ}\text{C unless otherwise specified)}$

| Parameter Parameter             | Symbol                  | Test Conditions         | Min   | Тур   | Max   | Unit         |

|---------------------------------|-------------------------|-------------------------|-------|-------|-------|--------------|

| Power Supply Section            |                         | 1                       | •     | • • • |       |              |

| VIN turn-on threshold           | $V_{VIN,ON}$            |                         |       | 14.7  |       | V            |

| VIN turn-off threshold          | $V_{VIN,OFF}$           |                         |       | 7     |       | V            |

| VIN OVP voltage                 | $V_{VIN,OVP}$           |                         |       | 17.5  |       | V            |

| Start up Current                | $I_{ST}$                | $V_{VIN} < V_{VIN,OFF}$ |       |       | 4     | μA           |

| Operating Current               | $I_{VIN}$               | $C_L=500pF, f=100kHz$   |       | 1     |       | mA           |

| Quiescent Current               | IQ                      | CL=0, f=2kHz            |       | 200   |       | μA           |

| Shunt current in OVP mode       | $I_{VIN,OVP}$           | $V_{VIN} > V_{VIN,OVP}$ |       | 7.5   |       | mA           |

| Current feedback modulator Se   | ection                  |                         |       |       |       |              |

| Internal reference voltage      | $V_{REF}$               |                         | -1.5% | 0.42  | +1.5% | V            |

| ISEN Sense Section              |                         |                         |       |       |       |              |

| Current limit reference voltage | V                       | $V_{FBV} < 0.4V$        |       | 0.7   |       | V            |

| Current mint reference voltage  | V <sub>ISEN,LIM</sub>   | $V_{FBV}>0.4V$          | -5%   | 1     | +5%   | V            |

| Latch Voltage for ISEN          | V <sub>ISEN,EX</sub>    |                         |       | 2     |       | V            |

| VSEN pin Section                |                         |                         |       |       |       |              |

| OVP voltage threshold           | $V_{VSEN,OVP}$          |                         | -5%   | 1.45  | +5%   | V            |

| VSEN pin voltage reference      | V <sub>VSEN,REF</sub>   |                         | -1.5% | 1.25  | +1.5% | V            |

| Cable Compensation coefficient  | K <sub>3</sub>          |                         |       | 17.5  |       | μA/V         |

| Gate Driver Section             |                         |                         |       |       |       | •            |

| Gate driver voltage             | $V_{Gate}$              |                         |       | 12    |       | V            |

| Maximum source current          | I <sub>SOURCE,MAX</sub> |                         |       | 120   |       | mA           |

| Maximum sink current            | I <sub>SINK,MAX</sub>   |                         |       | 500   |       | mA           |

| Max ON Time                     | $T_{ON,MAX}$            |                         |       | 24    |       | μs           |

| Min ON Time                     | $T_{ON,MIN}$            |                         |       |       | 300   | ns           |

| Max OFF Time                    | T <sub>OFF,MAX</sub>    |                         |       | 500   |       | μs           |

| Min OFF Time                    | $T_{OFF,MIN}$           |                         |       | 1.2   |       | μs           |

| Maximum switching frequency     | $f_{MAX}$               |                         |       | 125   |       | kHz          |

| Thermal Section                 |                         |                         |       |       |       |              |

| Thermal Shutdown Temperature    | $T_{SD}$                |                         |       | 150   |       | $^{\circ}$ C |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard. Test condition: Device mounted on 2" x 2" FR-4 substrate PCB, 2oz copper, with minimum recommended pad on top layer and thermal vias to bottom layer ground plane.

Note 3: Increase VIN pin voltage gradually higher than V<sub>VIN.ON</sub> voltage then turn down to 12V.

## **Operation**

SY5002C is a high performance Flyback controller with primary side control and constant current and constant voltage regulation.

The Device provides primary side control to eliminate the opto-isolators or the secondary feedback circuits, which would cut down the cost of the system.

In order to reduce the switching losses and improve EMI performance, Quasi-Resonant switching mode is applied, which turn ON the power MOSFET when the voltage across Drain and Source is at its lowest point; the start up current of the device is rather small (4 $\mu$ A typically) to reduce the standby power loss further.

In order to improve the stability, the self-adaption compensation is applied.

The device provides reliable protections such as Over Voltage Protection (OVP), Short Circuit Protection (SCP), Over Temperature Protection (OTP), Output voltage OVP protection, VSEN pin short protection, etc..

SY5002C can be applied in AC/DC adapters, Battery Chargers and other consumer electronics.

SY5002C is available with SOT23-6 package.

# **Applications Information**

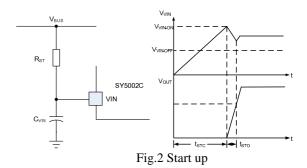

#### Start up

After AC supply or DC BUS is powered on, the capacitor  $C_{VIN}$  across VIN and GND pin is charged up by BUS voltage through a start up resistor  $R_{ST}$ . Once  $V_{VIN}$  rises up to  $V_{VIN-ON}$ , the internal blocks start to work.  $V_{VIN}$  will be pulled down by internal consumption of IC until the auxiliary winding of Flyback transformer could supply enough energy to maintain  $V_{VIN}$  above  $V_{VIN-OFF}$ .

The whole start up procedure is divided into two sections shown in Fig.2.  $t_{STC}$  is the  $C_{VIN}$  charged up section, and  $t_{STO}$  is the output voltage built-up section. The start up time  $t_{ST}$  composes of  $t_{STC}$  and  $t_{STO}$ , and usually  $t_{STO}$  is much smaller than  $t_{STC}$ .

The start up resistor  $R_{ST}$  and  $C_{VIN}$  are designed by rules below:

(a) Preset start-up resistor  $R_{ST}$ , make sure that the current through  $R_{ST}$  is larger than  $I_{ST}$  and smaller than  $I_{VIN\_OVP}$

$$\frac{V_{\scriptscriptstyle BUS}}{I_{\scriptscriptstyle VIN\_{\scriptscriptstyle OVP}}}{<}R_{\scriptscriptstyle ST}<\frac{V_{\scriptscriptstyle BUS}}{I_{\scriptscriptstyle ST}}\left(1\right)$$

Where  $V_{BUS}$  is the BUS line voltage.

**(b)** Select  $C_{VIN}$  to obtain an ideal start up time  $t_{ST}$ , and ensure the output voltage is built up at one time.

$$C_{VIN} = \frac{(\frac{V_{BUS}}{R_{ST}} - I_{ST}) \times t_{ST}}{V_{VIN\_ON}} (2)$$

(c) If the  $C_{VIN}$  is not big enough to build up the output voltage at one time. Increase  $C_{VIN}$  and decrease  $R_{ST}$ , go back to step (a) and redo such design flow until the ideal start up procedure is obtained.

#### Shut down

After AC supply or DC BUS is powered off, the energy stored in the BUS capacitor will be discharged. When the auxiliary winding of Flyback transformer can not supply enough energy to VIN pin,  $V_{\rm VIN}$  will drop down. Once  $V_{\rm VIN}$  is below  $V_{\rm VIN-OFF}$ , the IC will stop working.

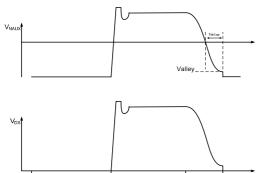

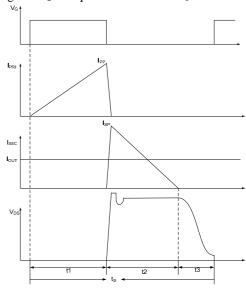

#### **Quasi-Resonant Operation(valley detection)**

QR mode operation provides low turn-on switching losses for Flyback converter.

Fig.3 QR mode operation

The voltage across drain and source of the primary MOSFET is reflected by the auxiliary winding of the Flyback transformer. VSEN pin detects the voltage across the auxiliary winding by a resistor divider. When the voltage on VSEN pin across zero, the MOSFET would be turned on after 400ns delay.

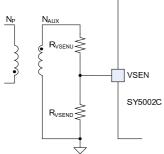

#### Output Voltage Control(CV control)

In order to achieve primary side constant voltage control, the output voltage is detected by the auxiliary winding voltage.

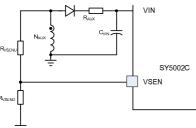

Fig.4 VSEN pin connection

As shown in Fig.5, during OFF time, the voltage across the auxiliary winding is

$$V_{AUX} = (V_{OUT} + V_{D-F}) \times \frac{N_{AUX}}{N_s}$$

(3)

$N_{AUX}$  is the turns of auxiliary winding;  $N_S$  is the turns of secondary winding;  $V_{D\text{-}F}$  is the forward voltage of the power diode.

At the current zero-crossing point,  $V_{\text{D-F}}$  is nearly zero, so  $V_{\text{OUT}}$  is proportional with  $V_{\text{AUX}}$  exactly. The voltage of this point is sampled by the IC as the feedback of output voltage. The resistor divider is designed by

$$\frac{V_{_{VSEN-REF}}}{V_{_{OUT}}} = \frac{R_{_{VSEND}}}{R_{_{VSENU}} + R_{_{VSEND}}} \times \frac{N_{_{AUX}}}{N_{_{S}}}$$

(4)

Where  $V_{\text{VSEN-REF}}$  is the internal voltage reference.

Fig.5 Auxiliary winding voltage waveforms

#### **Output Current Control(CC control)**

The output current is regulated by SY5002C with primary side detection technology, the maximum output current  $I_{\text{OUT-LIM}}$  can be set by

$$I_{OUT\text{-}LIM} = \frac{k_1 \times V_{REF} \times N_{PS}}{R_S}$$

(5)

Where  $k_1$  is the output current weight coefficient;  $V_{REF}$  is the internal reference voltage;  $R_S$  is the current sense resistor.

$k_1$  and  $V_{REF}$  are all internal constant parameters,  $I_{OUT\text{-}LIM}$  can be programmed by  $N_{PS}$  and  $R_S$ .

$$R_{s} = \frac{k_{1} \times V_{REF} \times N_{PS}}{I_{OUT}}$$

(6)

$K_1$  is set to 0.5

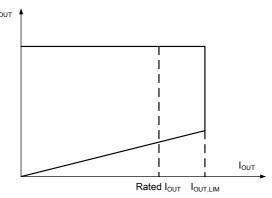

When over current operation or short circuit operation happens, the output current will be limited at  $I_{\text{OUT-LIM}}$ . The V-I curve is shown as Fig.6.

Fig.6 V-I curve

The IC provides line regulation modification function to improve line regulation performance of the output current.

Due to the sample delay of ISEN pin and other internal delay, the output current increases with increasing input BUS line voltage. A small compensation voltage  $\Delta V_{\rm ISEN-C}$  is added to ISEN pin during ON time to improve such performance. This  $\Delta V_{\rm ISEN-C}$  is adjusted by the upper resistor of the divider connected to VSEN pin.

$$\Delta V_{\text{ISEN-C}} = V_{\text{BUS}} \times \frac{N_{\text{AUX}}}{N_{\text{P}}} \times \frac{1}{R_{\text{VSENIU}}} \times k_2$$

(7)

Where  $R_{VSENU}$  is the upper resistor of the divider;  $k_2$  is an internal constant as the modification coefficient.

The compensation is mainly related with  $R_{VSENU}$ , larger compensation is achieved with smaller  $R_{VSENU}$ . Normally,  $R_{VSENU}$  ranges from  $50k\Omega{\sim}150k\Omega$ .

#### **Cable Compensation**

SY5002C has cable compensation to regulate the output voltage for better load regulation at cable terminal. When the converter output load increases from no load to full load, the voltage drops on the output cable are compensated by decreasing the voltage feedback signals, which is shown by Fig. 7.

Fig. 7 Cable Compensation

$$R_{Cable} = 2k_3 \cdot R_S \cdot \frac{N_S}{N_P} \cdot R_{VSENU} \cdot \frac{N_S}{N_{AUX}}$$

(8)

$k_3$  is set to 17.5  $\mu$  A/V

$R_{cable}$  is the resistance on the cable. The cable compensation effect can be adjusted by change the resistance of  $R_{VSENU}$  to achieve good load regulation of different output cables. The larger  $R_{VSENU}$ , the stronger cable compensation effect will be achieved.

If the output current is below 10% the OCP point, there is no cable compensation.

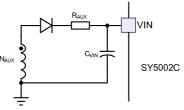

#### **Short Circuit Protection (SCP)**

There are two kinds of situations, one is the valley signal cannot be detected by VSEN, the other is the valley signal can be detected by VSEN.

When the output is shorted to ground, the output voltage is clamped to zero. The voltage of the auxiliary winding is proportional to the output winding, so valley signal cannot be detected by VSEN. There are two cases , the one is without valley detection, MOSFET cannot be turned on until maximum off time is reached. If MOSFET is turned on with maximum off-time for 64 times continuously which can not detected valley, IC will be shut down and enter into hiccup mode. The other is that IC will be shut down and enter into hiccup mode when  $V_{\rm VIN}$  below  $V_{\rm VIN-OFF}$  within 64 times .

When the output voltage is not low enough to disable valley detection in short condition, SY5002C will operate in CC mode until VIN is below V<sub>IN-OFF</sub>.

In order to guarantee SCP function not effected by voltage spike of auxiliary winding, a filter resistor  $R_{\text{AUX}}$  is needed.

Fig. 8 Filter resistor R<sub>AUX</sub>

#### **Output voltage OVP protection**

The secondary maximum voltage is limited by the SY5002C. When the VSEN pin signal exceeds 1.45V, SY5002C will stop switching and discharge the VIN

voltage. Once  $V_{\text{VIN}}$  is below  $V_{\text{VIN-OFF}}$ , the IC will shut down and be charged again by HV start up.

#### **VSEN** pin short protection

The SY5002C has a protection against faults caused by a shorted VSEN pin or a shorted pull-down resistor. During start-up, the voltage on the VSEN pin is monitored. In normal situations, the voltage on the VSEN pin reaches the sense protection trigger level. When the VSEN voltage does not reach this level, the VSEN pin is shorted and the protection is activated. The IC stops switching and discharge the VIN voltage. Once  $V_{\text{VIN}}$  is below  $V_{\text{VIN-OFF}}$ , the IC will shut down and be charged again by HV start up. In order to ensure reliable detection, the pull-down resistor should larger than  $2k\Omega$ .

### **Power Device Design**

#### **MOSFET and DIODE**

When the operation condition is with maximum input voltage and full load, the voltage stress of MOSFET and secondary power diode is maximized;

$$V_{\text{MOS\_DS\_MAX}} = \sqrt{2} V_{\text{AC\_MAX}} + N_{\text{PS}} \times (V_{\text{OUT}} + V_{\text{D\_F}}) + \Delta V_{\text{S}} (8)$$

$$V_{\text{D\_R\_MAX}} = \frac{\sqrt{2} V_{\text{AC\_MAX}}}{N_{\text{PS}}} + V_{\text{OUT}} (9)$$

Where  $V_{AC\text{-}MAX}$  is maximum input AC RMS voltage;  $N_{PS}$  is the turns ratio of the Flyback transformer;  $V_{OUT}$  is the rated output voltage;  $V_{D\text{-}F}$  is the forward voltage of secondary power diode;  $\Delta V_S$  is the overshoot voltage clamped by RCD snubber during OFF time.

When the operation condition is with minimum input voltage and full load, the current stress of MOSFET and power diode is maximized.

$$\begin{split} &\mathbf{I}_{\text{MOS\_PK\_MAX}}\!=&\mathbf{I}_{\text{P\_PK\_MAX}}\left(10\right)\\ &\mathbf{I}_{\text{MOS\_RMS\_MAX}}\!=&\mathbf{I}_{\text{P\_RMS\_MAX}}\left(11\right)\\ &\mathbf{I}_{\text{D\_PK\_MAX}}\!=&\mathbf{N}_{\text{PS}}\!\times&\mathbf{I}_{\text{P\_PK\_MAX}}\left(12\right)\\ &\mathbf{I}_{\text{D\_AVG}}\!=&\mathbf{I}_{\text{OUT}}\left(13\right) \end{split}$$

Where  $I_{P\text{-PK-MAX}}$  and  $I_{P\text{-RMS-MAX}}$  are maximum primary peak current and RMS current, which will be introduced later.

#### Transformer (N<sub>PS</sub> and L<sub>M</sub>)

$N_{PS}$  is limited by the electrical stress of the power MOSFET:

$$N_{PS} \le \frac{V_{MOS\_(BR)DS} \times 90\% - \sqrt{2}V_{AC\_MAX} - \Delta V_{S}}{V_{OUT} + V_{D\_F}}$$

(14)

Where  $V_{MOS,(BR)DS}$  is the breakdown voltage of the power MOSFET.

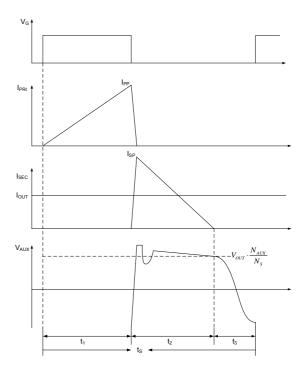

In Quasi-Resonant mode, each switching period cycle t<sub>S</sub> consists of three parts: current rising time t<sub>1</sub>, current falling time t<sub>2</sub> and quasi-resonant time t<sub>3</sub> shown in Fig.9.

Fig.9 switching waveforms

When the operation condition is with minimum input AC RMS voltage and full load, the switching frequency is minimum frequency, the maximum peak current through MOSFET and the transformer happens.

Once the minimum frequency  $f_{S\text{-MIN}}$  is set, the inductance of the transformer could be induced. The design flow is shown as below:

(a)Select N<sub>PS</sub>

$$N_{PS} \le \frac{V_{MOS\_(BR)DS} \times 90\% - \sqrt{2}V_{AC\_MAX} - \Delta V_{S}}{V_{OUT} + V_{DF}}$$

(15)

- (b) Preset minimum frequency f<sub>S-MIN</sub>

- (c) Compute inductor  $L_M$  and maximum primary peak current  $I_{P\text{-PK-MAX}}$

$$\begin{split} I_{P\_PK\_MAX} &= \frac{2P_{OUT}}{\eta \times V_{DC\_MIN}} + \frac{2P_{OUT}}{\eta \times N_{PS} \times (V_{OUT} + V_{D\_F})} (16) \\ &+ \pi \sqrt{\frac{2P_{OUT}}{\eta} \times C_{Drain} \times f_{S\_MIN}} \\ L_{m} &= \frac{2P_{OUT}}{\eta \times I_{P\_PK\_MAX}^{2} \times f_{S\_MIN}} (17) \end{split}$$

Where  $C_{Drain}$  is the parasitic capacitance at drain of MOSFET;  $\eta$  is the efficiency;  $P_{OUT}$  is rated full load power

(d) Compute current rising time  $t_1$  and current falling time  $t_2$

$$t_{1} = \frac{L_{M} \times I_{P_{-}PK_{-}MAX}}{V_{BUS}} (18)$$

$$t_{2} = \frac{L_{m} \times I_{P_{-}PK_{-}MAX}}{N_{PS} \times (V_{OUT} + V_{D_{-}F})} (19)$$

$$t_{S} = \frac{1}{f_{S_{-}MIN}} (20)$$

(e) Compute primary maximum RMS current  $I_{P-RMS-MAX}$  for the transformer fabrication.

$$I_{P_{-RMS_{-}MAX}} = \frac{\sqrt{3}}{3} I_{P_{-PK_{-}MAX}} \times \sqrt{\frac{t_1}{t_s}}$$

(21)

(f) Compute secondary maximum peak current  $I_{S\text{-PK-MAX}}$  and RMS current  $I_{S\text{-RMS-MAX}}$  for the transformer fabrication.

$$I_{S\_PK\_MAX} = N_{PS} \times I_{P\_PK\_MAX} (22)$$

$$I_{S\_RMS\_MAX} = \frac{\sqrt{3}}{3} N_{PS} \cdot I_{P\_PK\_MAX} \cdot \sqrt{\frac{t_2}{t_S}} (23)$$

#### Transformer design (N<sub>P</sub>,N<sub>S</sub>,N<sub>AUX</sub>)

The design of the transformer is similar with ordinary Flyback transformer. the parameters below are necessary:

| Necessary parameters          |                        |

|-------------------------------|------------------------|

| Turns ratio                   | $N_{PS}$               |

| Inductance                    | $L_{M}$                |

| Primary maximum current       | $I_{P-PK-MAX}$         |

| Primary maximum RMS current   | $I_{P-RMS-MAX}$        |

| Secondary maximum RMS current | I <sub>S-RMS-MAX</sub> |

The design rules are as followed:

- (a) Select the magnetic core style, identify the effective area  $A_{\text{e.}}$

- (b) Preset the maximum magnetic flux  $\Delta B$

$\Delta B = 0.22 \sim 0.26T$

(c) Compute primary turn N<sub>P</sub>

$$N_{p} = \frac{L_{M} \times I_{P\_PK\_MAX}}{\Delta B \times A_{e}} (24)$$

(d) Compute secondary turn N<sub>S</sub>

$$N_{\rm S} = \frac{N_{\rm P}}{N_{\rm PS}} (25)$$

(e) compute auxiliary turn N<sub>AUX</sub>

$$N_{AUX} = N_S \times \frac{V_{VIN}}{V_{OUT}}$$

(26)

Where  $V_{VIN}$  is the working voltage of VIN pin (11V~15V is recommended).

(f) Select an appropriate wire diameter

With  $I_{P-RMS-MAX}$  and  $I_{S-RMS-MAX}$ , select appropriate wire to make sure the current density ranges from  $4A/mm^2$  to  $10A/mm^2$

(g) If the winding area of the core and bobbin is not enough, reselect the core style, go to (a) and redesign the transformer until the ideal transformer is achieved.

#### **Input capacitor CBUS**

Generally, the input capacitor C<sub>BUS</sub> is selected by

$$C_{BUS} = 2 \sim 3\mu F/W$$

Or more accurately by

$$C_{\text{BUS}} = \frac{\arcsin(1 - \frac{\Delta V_{\text{BUS}}}{\sqrt{2} V_{\text{AC\_MIN}}}) + \frac{\pi}{2}}{\pi} \times \frac{P_{\text{OUT}}}{\eta} \times \frac{1}{2f_{\text{IN}} V_{\text{AC\_MIN}}^2 [1 - (1 - \frac{\Delta V_{\text{BUS}}}{\sqrt{2} V_{\text{AC\_MIN}}})^2]}$$

(27)

Where  $\Delta V_{BUS}$  is the voltage ripple of BUS line.

#### **RCD** snubber for MOSFET

The power loss of the snubber P<sub>RCD</sub> is evaluated first

$$P_{\text{RCD}} = \frac{N_{\text{PS}} \times (V_{\text{OUT}} + V_{\text{D\_F}}) + \Delta V_{\text{S}}}{\Delta V_{\text{s}}} \times \frac{L_{\text{K}}}{L_{\text{M}}} \times P_{\text{OUT}}$$

(28)

Where  $N_{PS}$  is the turns ratio of the Flyback transformer;  $V_{OUT}$  is the output voltage;  $V_{D\text{-}F}$  is the forward voltage of the power diode;  $\Delta V_S$  is the overshoot voltage clamped by RCD snubber;  $L_K$  is the leakage inductor;  $L_M$  is the inductance of the Flyback transformer;  $P_{OUT}$  is the output power.

The R<sub>RCD</sub> is related with the power loss:

$$R_{_{RCD}} = \frac{(N_{_{PS}} \times (V_{_{OUT}} + V_{_{D\_F}}) + \Delta V_{_{S}})^2}{P_{_{RCD}}} (29)$$

The  $C_{\text{RCD}}$  is related with the voltage ripple of the snubber  $\Delta V_{\text{C-RCD}}\text{:}$

$$C_{\text{RCD}} = \frac{N_{\text{PS}} \times (V_{\text{OUT}} + V_{\text{D\_F}}) + \Delta V_{\text{S}}}{R_{\text{RCD}} f_{\text{S}} \Delta V_{\text{C} \text{ RCD}}} (30)$$

## Layout

- (a) To achieve better EMI performance and reduce line frequency ripples, the output of the bridge rectifier should be connected to the BUS line capacitor first, then to the switching circuit.

- (b) The circuit loop of all switching circuit should be kept small: primary power loop, secondary loop and auxiliary power loop.

- (c) The connection of primary ground is recommended as:

- Ground ①: ground of BUS line capacitor

- Ground ②: ground of bias supply capacitor

- Ground ③: ground node of auxiliary winding

- Ground 4: ground node of divider resistor

- Ground (5): primary ground node of Y capacitor

- Ground 6: ground node of current sample resistor.

- Ground ⑦: ground of IC GND.

- (d) bias supply trace should be connected to the bias supply capacitor first instead of GND pin. The bias supply capacitor should be put beside the IC.

- (e) Loop of 'Source pin current sample resistor GND pin' should be kept as small as possible.

- (f) The resistor divider connected to VSEN pin is recommended to be put beside the IC.

Note: Ground node of current sample resistor must be connected to the ground of bus line capacitor

### **Design Notice**

- 1. At no load, secondary side diode freewheeling time should be more than 1.8us.

- 2. VIN voltage prefer to larger than 11V for all conditions.

- 3. Some transformers structure may induce larger spike or larger ring on the current sample resistor at the initial of the primary switch turning on. This spike or ring may cause wrongly detection of the peak current and make The switch turn off earlier, so the accuracy feedback voltage sample cannot be guaranteed. The recommend structures are: 0.5Pri.---shielding----Sec.----Aux.---0.5Pri.or Pri.----shielding----Sec.----Aux.; Do not use the structure like 0.5Pri.----Aux----Sec.----Shielding.----0.5Pri.

- 4. RCD snubber's influence:

- At no load and light load, capacitor's voltage may be discharged to a small value, when primary switch turn off, peak current needs to charge the snubber capacitor, this will affect the feedback voltage sample and include larger ripple or other issues. The recommend parameters is: When Imin(Imin=0.15V/Rs) is 0.1A, the snubber capacitor should not larger than 470pF.

- 5. At heavy load, the peak-to-peak voltage at the VSEN pin should be less than approximately 100mVp-p after off-min time(1.8us). This can be guaranteed by decreasing the leakage inductance and using proper RCD snubber.

- 6.  $R_{VSENU}$  is the upper resistor of the divider .Normally, its value should be in  $50k\Omega \sim 150k\Omega$ .

### **Design Example**

A design example of typical application is shown below step by step.

#### #1. Identify design specification

| Design Specification |          |                  |     |

|----------------------|----------|------------------|-----|

| $V_{AC}(RMS)$        | 90V~264V | V <sub>OUT</sub> | 12V |

| $I_{OUT}$            | 2A       | η                | 90% |

#### #2. Transformer design $(N_{PS}, L_M)$

#### Refer to Power Device Design

| Conditions             |                |                    |       |

|------------------------|----------------|--------------------|-------|

| $V_{AC,MIN}$           | 90V            | $V_{AC-MAX}$       | 264V  |

| $\Delta V_{S}$         | 75V            | $V_{MOS-(BR)DS}$   | 600V  |

| P <sub>OUT</sub> (max) | 24W            | $V_{\mathrm{D,F}}$ | 1V    |

| $C_{Drain}$            | 100pF          | $f_{S-MIN}$        | 60kHz |

| $\Delta V_{BUS}$       | $30\% V_{BUS}$ |                    |       |

#### (a)Compute turns ratio N<sub>PS</sub> first

$$\begin{split} N_{PS} &\leq \frac{V_{MOS\_(BR)DS} \times 90\% - \sqrt{2}V_{AC\_MAX} - \Delta V_{S}}{V_{OUT} + V_{D,F}} \\ &= \frac{600V \times 0.9 - \sqrt{2} \times 264V - 75V}{12V + 1V} \\ &= 7.05 \end{split}$$

N<sub>PS</sub> is set to

$$N_{PS} = 7$$

(b)f<sub>S,MIN</sub> is preset

$$f_{S MIN} = 60kHz$$

(c) Compute inductor  $L_{\text{M}}$  and maximum primary peak current  $I_{\text{P,PK,MAX}}$

$$\begin{split} I_{P\_PK\_MAX} &= \frac{2P_{OUT}}{\eta \times \left(\sqrt{2}V_{AC\_MIN} - \Delta V_{BUS}\right)} + \frac{2P_{OUT}}{\eta \times N_{PS} \times (V_{OUT} + V_{D\_F})} + \pi \sqrt{\frac{2P_{OUT}}{\eta}} \times C_{Drain} \times f_{S\_MIN} \\ &= \frac{2 \times 24W}{0.9 \times (\sqrt{2} \times 90V - 0.3 \times \sqrt{2} \times 90V)} + \frac{2 \times 24W}{0.9 \times 7 \times (12V + 1V)} + \pi \times \sqrt{\frac{2 \times 24W}{0.9} \times 100pF \times 60KHz} \\ &= 1.241A \\ L_m &= \frac{2P_{OUT}}{\eta \times I_{P\_PK\_MAX}^2 \times f_{S\_MIN}} \\ &= \frac{2 \times 24W}{0.9 \times (1.241A)^2 \times 60KHz} \\ &= 0.577mH \end{split}$$

Set:  $L_m=0.55mH$

(d) Compute current rising time t<sub>1</sub> and current falling time t<sub>2</sub>

$$t_{_{1}} = \frac{L_{_{M}} \times I_{_{P\_PK\_MAX}}}{V_{_{BUS}}} = \frac{0.55 \text{mH} \times 1.241 \text{A}}{\sqrt{2} \times 90 \text{V}} = 5.36 \mu \text{s}$$

$$t_{2} = \frac{L_{m} \times I_{P_{-}PK_{-}MAX}}{N_{PS} \times (V_{OUT} + V_{D_{-}F})} = \frac{0.55mH \times 1.241A}{7 \times (12V + 1V)} = 7.5\mu s$$

$$t_{_{3}}\!=\!\pi\!\times\!\sqrt{L_{_{M}}\!\times\!C_{_{Drain}}}\!=\!\pi\!\times\!\sqrt{0.55mH\!\times\!100pF}\!=\!0.737\mu s$$

$$t_s = t_1 + t_2 + t_3 = 5.36\mu s + 7.5\mu s + 0.737\mu s = 13.6\mu s$$

(e) Compute primary maximum RMS current  $I_{P\text{-}RMS\text{-}MAX}$  for the transformer fabrication.

$$I_{P_{-RMS\_MAX}} = \frac{\sqrt{3}}{3} I_{P_{-PK\_MAX}} \times \sqrt{\frac{t_1}{t_s}} = \frac{\sqrt{3}}{3} \times 1.241 A \times \sqrt{\frac{5.36 \mu s}{13.6 \mu s}} = 0.45 A$$

(f) Compute secondary maximum peak current I<sub>S-PK-MAX</sub> and RMS current I<sub>S-RMS-MAX</sub> for the transformer fabrication.

$$I_{S\_PK\_MAX} = N_{PS} \times I_{P\_PK\_MAX} = 7 \times 1.241A = 8.686A$$

$$I_{S\_RMS\_MAX} = N_{PS} \times \frac{\sqrt{3}}{3} I_{P\_PK\_MAX} \times \sqrt{\frac{t_2}{t_S}} = 7 \times \frac{\sqrt{3}}{3} \times 1.241 A \times \sqrt{\frac{7.5 \mu s}{13.6 \mu s}} = 3.724 A$$

#3. Select power MOSFET and secondary power diode

Refer to Power Device Design

| Known conditions at this step |     |           |    |  |  |

|-------------------------------|-----|-----------|----|--|--|

| $V_{AC-MAX}$ 264V $N_{PS}$ 7  |     |           |    |  |  |

| V <sub>OUT</sub>              | 12V | $V_{D-F}$ | 1V |  |  |

| $\Delta V_{\mathrm{S}}$       | 75V |           |    |  |  |

(a) Compute the voltage and the current stress of MOSFET:

$$\begin{aligned} V_{\text{MOS\_DS\_MAX}} = & \sqrt{2} V_{\text{AC\_MAX}} + N_{\text{PS}} \times (V_{\text{OUT}} + V_{\text{D\_F}}) + \Delta V_{\text{S}} \\ = & \sqrt{2} \times 264 V + 7 \times (12 V + 1 V) + 75 V \\ = & 539 V \end{aligned}$$

$$I_{MOS\ PK\ MAX} = I_{P\ PK\ MAX} = 1.241A$$

$$I_{MOS\ RMS\ MAX} = I_{P\ RMS\ MAX} = 0.45A$$

(b) Compute the voltage and the current stress of secondary power diode

$$V_{D_{\_R\_MAX}} = \frac{\sqrt{2}V_{AC\_MAX}}{N_{PS}} + V_{OUT}$$

$$= \frac{\sqrt{2} \times 264V}{7} + 12V$$

$$= 65.3V$$

$$I_{D_{PK\_MAX}} = N_{PS} \times I_{P_{PK\_MAX}} = 7 \times 1.241A = 8.686A$$

$$I_{\scriptscriptstyle D\_AVG}\!=\!2A$$

#4. Select the input capacitor C<sub>IN</sub>

Refer to input capacitor C<sub>IN</sub> Design

|   | Known conditions at this step |     |                          |                   |  |

|---|-------------------------------|-----|--------------------------|-------------------|--|

| 1 | $V_{AC,MIN}$                  | 90V | $\Delta { m V}_{ m BUS}$ | $30\% V_{AC,MIN}$ |  |

$$C_{\text{BUS}} = \frac{\arcsin(1 - \frac{\Delta V_{\text{BUS}}}{\sqrt{2} V_{\text{AC\_MIN}}}) + \frac{\pi}{2}}{\pi} \times \frac{P_{\text{OUT}}}{\eta} \times \frac{1}{2f_{\text{IN}} V_{\text{AC\_MIN}}^2 [1 - (1 - \frac{\Delta V_{\text{BUS}}}{\sqrt{2} V_{\text{AC\_MIN}}})^2]}$$

$$= \frac{\arcsin(1 - \frac{0.3 \times \sqrt{2} \times 90 \text{V}}{\sqrt{2} \times 90 \text{V}}) + \frac{\pi}{2}}{\pi} \times \frac{24 \text{W}}{0.9} \times \frac{1}{2 \times 50 \text{Hz} \times 90 \text{V}^2 \times [1 - (1 - \frac{0.3 \times \sqrt{2} \times 90 \text{V}}{\sqrt{2} \times 90 \text{V}})^2]}$$

$$= 48.2 \text{uF}$$

$=48.2 \mu F$

Set C<sub>BUS</sub>

$C_{BUS} = 44uF$

Where  $\Delta V_{BUS}$  is the voltage ripple of BUS line.

#5. Set VIN pin

Refer to Start up

| Conditions              |                       |                    |                        |  |  |  |

|-------------------------|-----------------------|--------------------|------------------------|--|--|--|

| $V_{ m BUS\text{-}MIN}$ | $90V \times \sqrt{2}$ | $V_{BUS-MAX}$      | $264V \times \sqrt{2}$ |  |  |  |

| $I_{ST}$                | 4μA (typical)         | $V_{\text{IN-ON}}$ | 14.7V (typical)        |  |  |  |

| $I_{VIN-OVP}$           | 7.5mA (typical)       | $t_{ST}$           | 2s (designed by user)  |  |  |  |

### (a) R<sub>ST</sub> is preset

$$R_{_{ST}} \! < \! \frac{V_{_{BUS}}}{I_{_{ST}}} \! = \! \frac{90V \! \times \! 1.414}{4 \mu A} \! = \! 31.81 M\Omega \; , \label{eq:R_ST}$$

$$R_{_{ST}} \! > \! \frac{V_{_{BUS}}}{I_{_{VIN\_OVP}}} \! = \! \frac{264V \! \times \! 1.414}{7.5 mA} \! = \! 49.77 k\Omega$$

Set R<sub>ST</sub>

$$R_{ST} = 4M$$

(b) Design C<sub>VIN</sub>

$$C_{_{VIN}}\!=\!\frac{(\frac{V_{_{BUS}}}{R_{_{ST}}}\!\!-\!\!I_{_{ST}})\!\!\times\!t_{_{ST}}}{V_{_{VIN\_{_{ON}}}}}\!=\!\frac{(\frac{90V\!\times\!1.414}{6M\Omega}\!\!-\!\!4\mu\!A)\!\!\times\!2s}{14.7V}\!\!=\!\!2.34\mu\!F$$

Set C<sub>VIN</sub>

$$C_{VIN} = 3.3 \mu F$$

#6. Set current sense resistor to achieve ideal output current

#### Refer to Primary-side constant-current control

| Known conditions at this step |       |               |      |  |  |  |

|-------------------------------|-------|---------------|------|--|--|--|

| $k_1$ 0.5 $N_{PS}$ 7          |       |               |      |  |  |  |

| $V_{REF}$                     | 0.42V | $I_{OUT,LIM}$ | 2.4A |  |  |  |

The current sense resistor is

$$\begin{split} R_{S} &= \frac{k_{_{1}} \times V_{_{REF}} \times N_{_{PS}}}{I_{_{OUT}}} \\ &= \frac{0.5 \times 0.42 V \times 7}{2.4 A} \\ &= 0.613 \Omega \end{split}$$

Set Rs

$Rs=0.556\Omega$

#7. Set VSEN pin

Refer to  $V_{\text{OUT}}$

First compute R<sub>VSENU</sub>

| Conditions         |      |                 |          |

|--------------------|------|-----------------|----------|

| V <sub>OUT</sub>   | 12V  | $V_{VSEN\_REF}$ | 1.25V    |

| R <sub>Cable</sub> | 0.2Ω | N <sub>S</sub>  | 13       |

| N <sub>AUX</sub>   | 15   | K <sub>3</sub>  | 17.5uA/V |

$$R_{v_{SENU}} = \frac{N_{P}}{N_{S}} \cdot R_{Cable} \cdot \frac{N_{AUX}}{N_{S}} \cdot \frac{1}{2K_{3} \cdot R_{S}} = 83K\Omega$$

$Set \; R_{VSENU}$

$$R_{VSENU} = 82k\Omega$$

Then compute  $R_{\text{VSEND}}$

$$R_{\text{VSEND}} = \frac{R_{\text{VSENU}}}{\frac{V_{\text{OUT}}N_{\text{AUX}}}{V_{\text{VSEN\_REF}}N_{\text{S}}} - 1} = \frac{100K}{(\frac{12V \times 15}{1.25V \times 13} - 1)} = 8.14K$$

$$R_{VSEND} = 8.2 k\Omega$$

#8. Final result

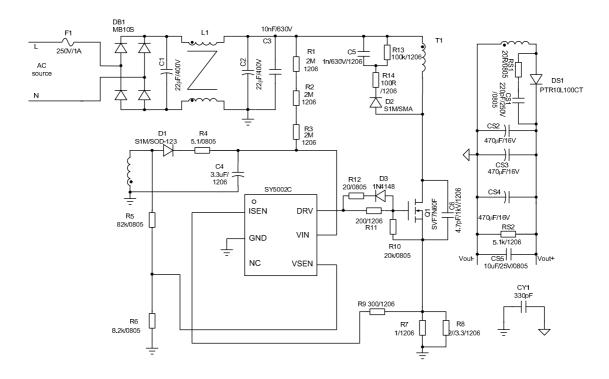

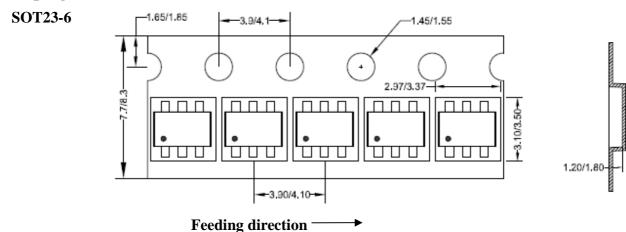

# SOT23-6 Package outline & PCB layout design

Notes: All dimensions are in millimeters.

All dimensions don't include mold flash & metal burr.

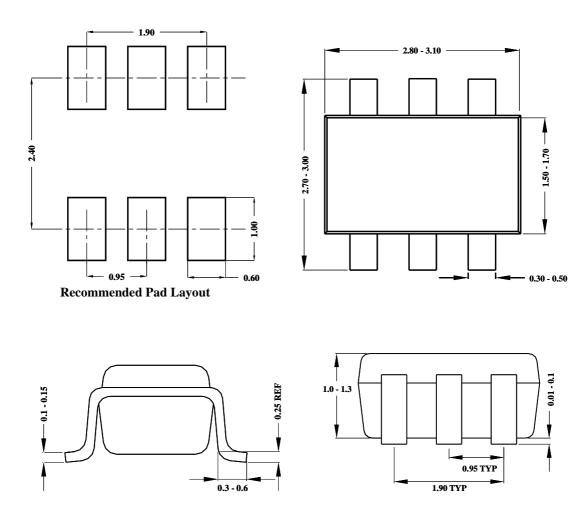

# **Taping & Reel Specification**

# 1. Taping orientation

# 2. Carrier Tape & Reel specification for packages

| Package<br>types | Tape<br>width<br>(mm) | Pocket<br>pitch(mm) | Reel size<br>(Inch) | Reel<br>width(mm) | Trailer<br>length(mm) | Leader length (mm) | Qty per<br>reel |

|------------------|-----------------------|---------------------|---------------------|-------------------|-----------------------|--------------------|-----------------|

| SOT23-6          | 8                     | 4                   | 7''                 | 8.4               | 280                   | 160                | 3000            |

### 3. Others: NA